INFN - Milano University of Milano Department of Physics

# Latest results in ASIC developments for TRACE and other detectors for nuclear physics research

Stefano Capra

"PhD Workshop 2013"

Oct. 14, 2013

- Context and goal of the research

- TRACE detectors & required specs for charge preamps

- From "Fast Reset" preamplifier to "Fast Reset" multichannel

- Non linear pole zero compensation technique

- Micro probe preamplifier: a completely new concept of preamplifier

- Conclusions

### Context

- New generation of nuclear-physics experiments with secondary radioactive beams.

- A technical advance for the FEE applied to the new highly segmentated telescopic silicon detector is required.

## Goal of the research

High-resolution spectroscopy of charged particles implementing a FEE based on a dedicated ASIC multichannel CSP

- Operated at room temperature (no need for cryogenic temperatures)

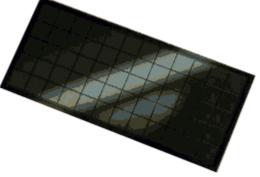

- Detector thickness: E pad **1.5mm**,  $\Delta E$  pad **200µm**

Silicon PAD detectors - main features:

- Single pad capacitance value: ~ from 2 pF to 15 pF

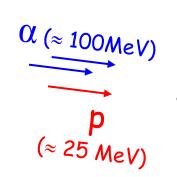

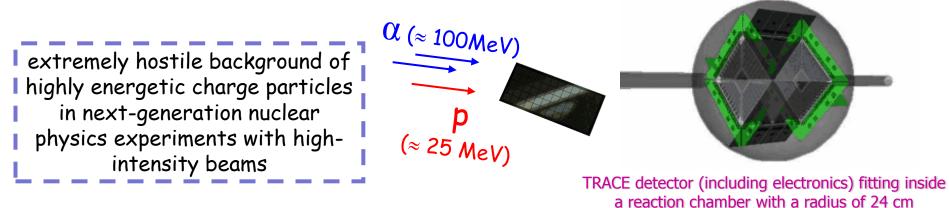

- Energy dynamics for detected particles: ~ **100 MeV** for  $\alpha$  particles, **25 MeV** for protons

- Intrinsic energy resolution: 40 keV @ 5.5 MeV for  $\alpha$  particles in 200  $\mu$ m detector

- Segmentation: ~ 4x4 mm geometry (also 8x8mm)

#### High-resolution particle spectroscopy : investigation of nuclear structure approaching the two extreme regions of proton and neutron drip lines

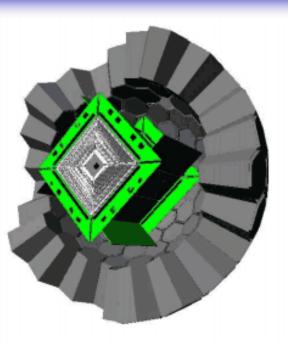

# TRACE detector

- Fit inside a sphere of 24 cm of diameter

- All the FEE electronics must fit inside the same volume

- Rise time of ~ 25 ns for 200  $\mu$ m thick  $\Delta$ E layer

- Transparent to  $\gamma$  radiation: coupled with  $\gamma$  spectrometer

- ~ 10000 output channels

- $4\pi$  configuration

- 4x4 mm and 8x8 mm segmentation

- Detection of light charged particles, neutron, heavy ions

- Particle discrimination and gamma doppler correction

- Decay spectroscopy

TRACE detector (including electronics) fitting inside AGATA 2π

- low noise (no more broadening than the intrinsic one)

- Few mW of single channel power consumption

- excellent stability of the gain and of the shape of the preamplifier response (loop gain~10<sup>3</sup>)

- wide bandwidth: rise time of ~ 10 ns (pulse shape analysis)

- low power consumption (large number of channels operated in vacuum)

- LARGE DYNAMIC RANGE:

- at least ~10<sup>5</sup> : from a few keV to 100-200 MeV (or above)

- minimization of the dead time in a larger energy range up to some hundreds of MeV

# Old-style solution: hybrid DISCRETE preamplifiers • high flexibility in the design

- use of high voltage power supply (ex: +/- 12 V)

- Absolutely unusable in this context

#### Modern CMOS integrated solutions: a mandatory task

The high segmentation of the detectors yields a higher and higher count of read-out channels (7k - 10k)

- small dimensions (very little space is available for FEE)

- radio-purity

- Low power consumption (operated in vacuum)

- Voltage power supply limited to +/- 2.6 V (limited dynamic range)

- Need for a multichannel ASIC solution

From "Fast Reset" preamplifier To "Fast Reset Multichannel"

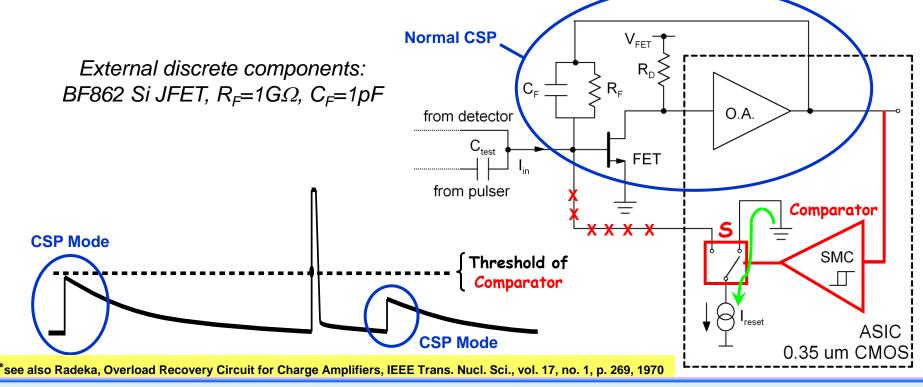

#### **Charge-Sensitive Preamplifier (CSP) Mode**

- For "normal" amplitude signals (up to a few MeV) the comparator keeps switch "S" in the right position

- The circuit is a Low-Noise Charge-sensitive preamplifier

- Allows for high-resolution energy measurements

Speaker: Stefano Capra

PhD Workshop 2013

From "Fast Reset" preamplifier To "Fast Reset Multichannel"

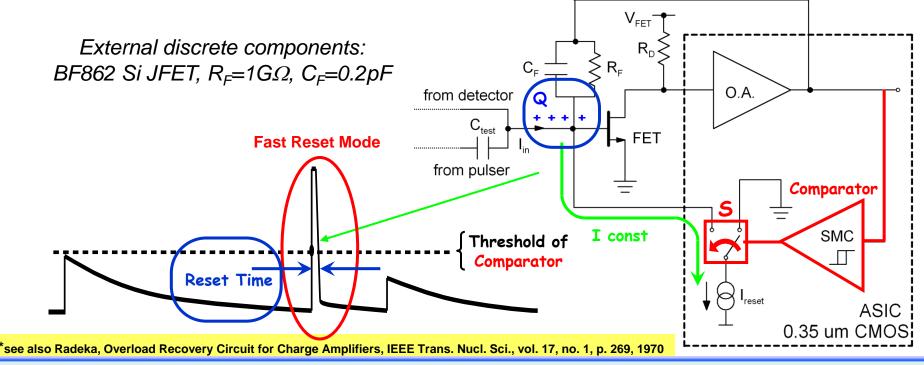

#### Fast-Reset Mode

- Minimizes the preamplifier **dead time** and prevents from the paralysis of the acquisition system in the case of extremely high background counting rates

- Allows for charge information even in the saturation condition

- Allows for high-resolution energy measurements → extending the dynamic range of photons/particles spectroscopy

Speaker: Stefano Capra

PhD Workshop 2013

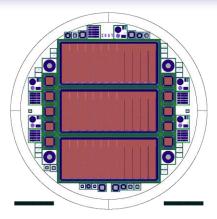

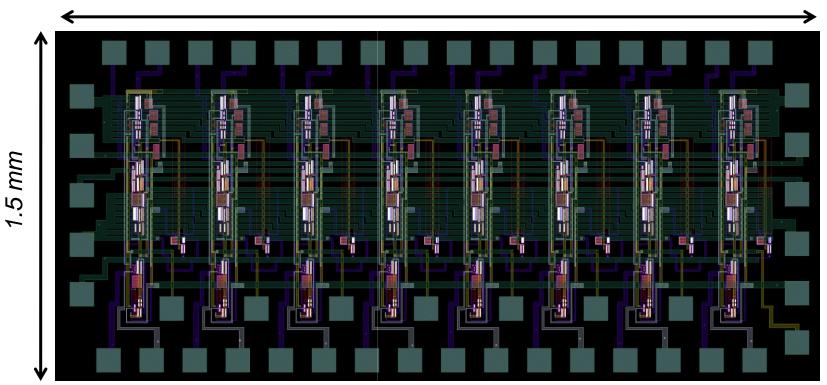

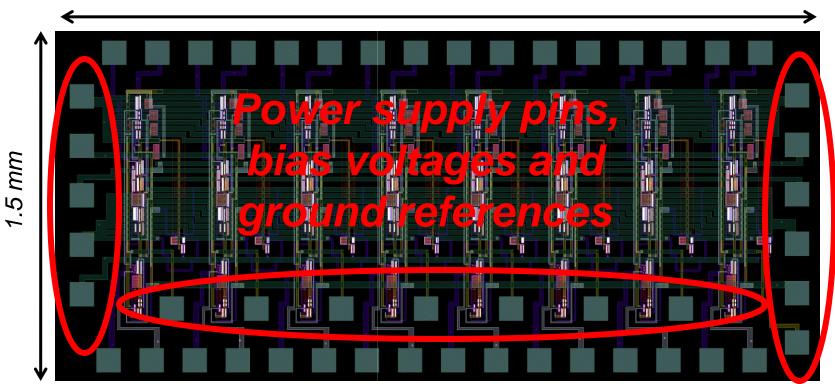

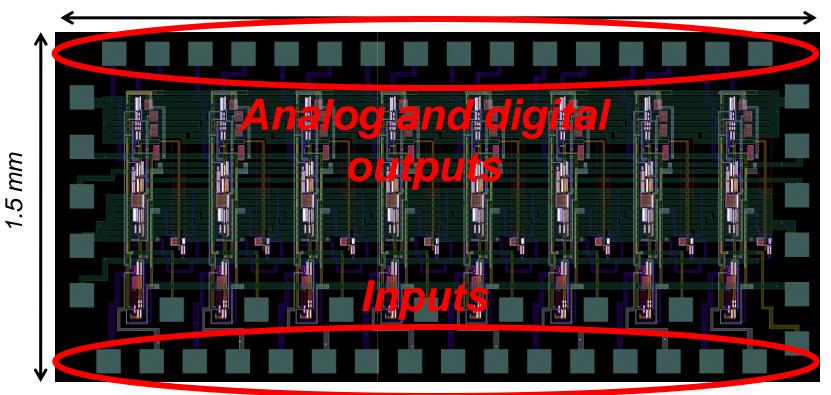

The first realization of the ASIC implements a discrete input stage (BF862) and discrete feedback loop (capacitor and discharge resistance)

3 mm

Layout 0.35 $\mu$ m 5V mid-oxide CMOS

Multichannel device

The first realization of the ASIC implements a discrete input stage (BF862) and discrete feedback loop (capacitor and discharge resistance)

Layout 0.35µm 5V mid-oxide CMOS

3 mm

Multichannel device

The first realization of the ASIC implements a discrete input stage (BF862) and discrete feedback loop (capacitor and discharge resistance)

*Layout 0.35µm 5V mid-oxide CMOS*

3 mm

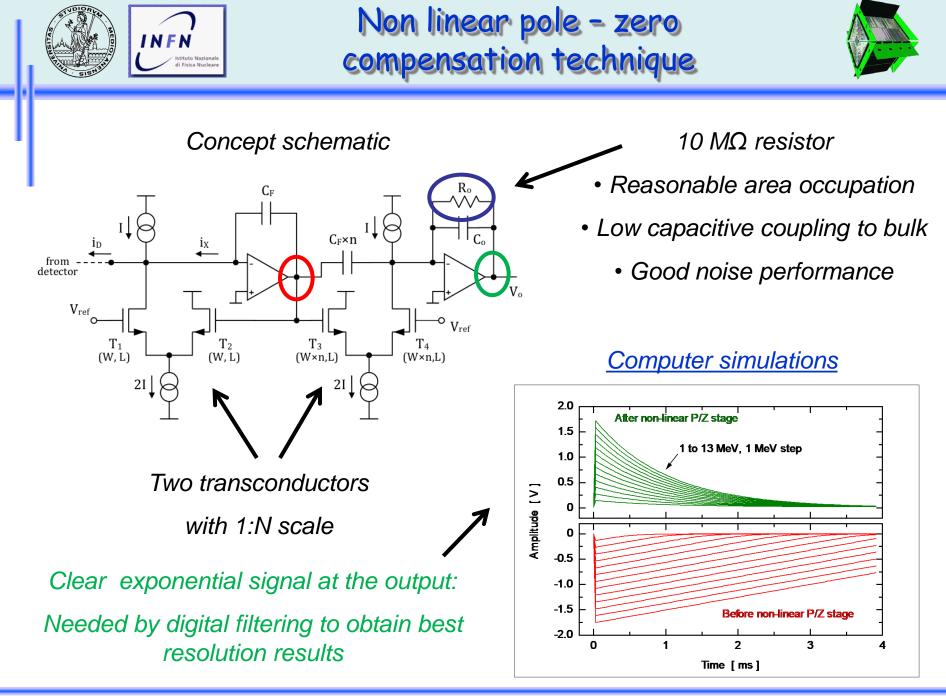

#### In order to provide low ENC the feedback resistance must be as high as possible

- Common choice for gamma-grade spectroscopy is  $1G\Omega$

- It would occupy an area of 2mm<sup>2</sup>

#### Common methods for substituting the feedback resistor

- High underthreshold CMOS structure (NOISE OK / LINEARITY PROBLEMS)

- Linear CMOS transconductor (LINEARITY OK / NOISE PROBLEMS)

Need for a new structure with provides both linearity and good noise performance, with limited area and power consumption

Speaker: Stefano Capra

PhD Workshop 2013

Speaker: Stefano Capra

PhD Workshop 2013

- Design, layout & computer simulation of a JFET-CMOS multichannel preamplifier (0.35µm) for Si pad - detectors equipped with a fast reset device for charge sensing stage de-saturation

- Design & computer simulation of the innovative non linear pole – zero compensation technique, which is a great step forward to the total integration of the ASIC CSP.

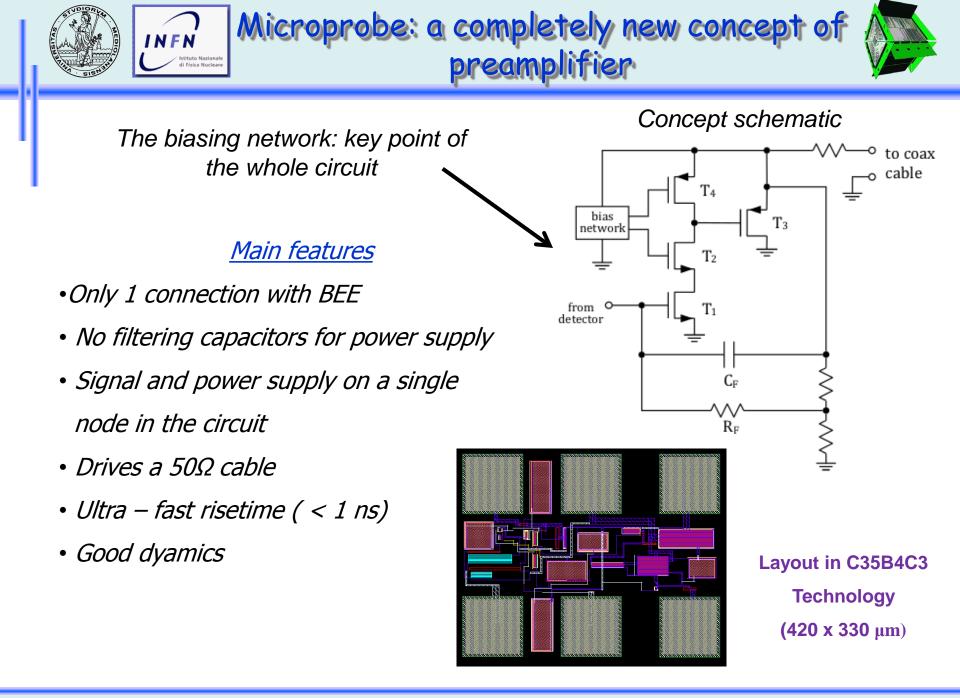

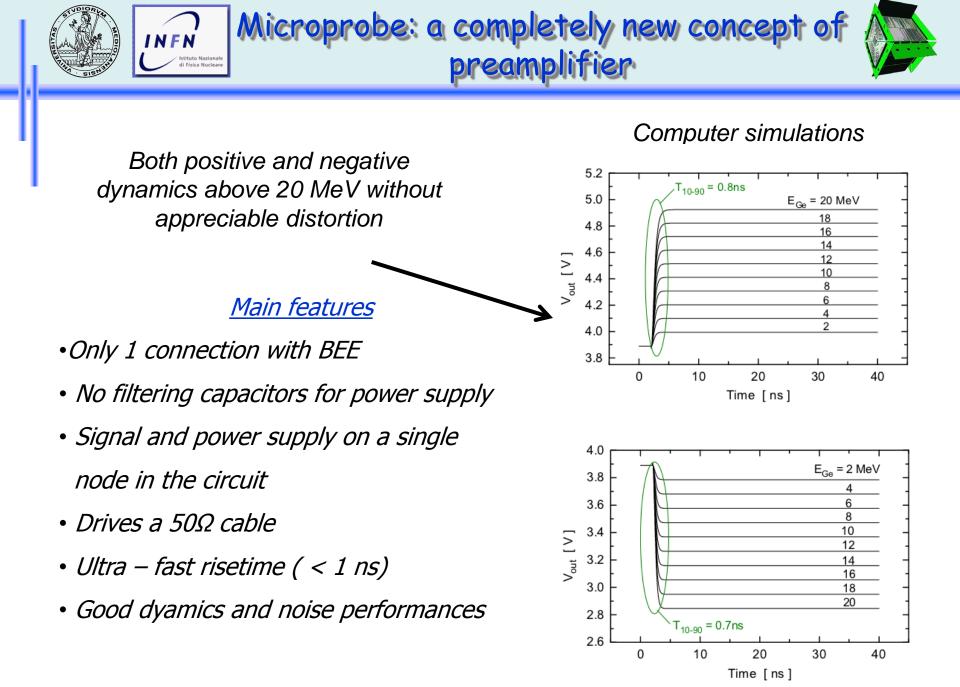

- Design, layout & simulation of a non conventional CSP device without power rails and a single power – signal connection to the BEE.

- Layout submission on 21th October 2013: experimental results on realized chips coming soon